氮化镓已成为事实上的第三代半导体材料。然而,以你需要的质量和所需的热阻制造 GaN 晶圆是晶圆厂仍在努力克服的挑战。

GaN外延层与硅、蓝宝石、碳化硅等衬底的晶格常数和热膨胀系数的不匹配导致外延层的位错和开裂。

一种常见的热管理方法是使用具有高导热性的基板(例如 SiC 或金刚石)作为散热器。然而,GaN和SiC/金刚石之间的晶格失配和热膨胀系数失配使得异质外延非常具有挑战性。此外,传统的成核层由于缺陷和结晶度差而表现出低导热率。具有低导热率的厚缓冲层为从器件到基板的散热路径增加了显着的热阻,因为大部分热量是在顶部的有源层内产生的。过渡层内、衬底和过渡层之间的界面处的缺陷和边界散射以及近界面无序共同促成了大的热阻。

尽管可以选择用于生长 GaN Epi 的衬底,但有些衬底对代工不友好,因此使用了 CMOS 工艺。另一个原因是,用于制造 CMOS 器件的最先进的光刻工具和其他工具只能在更大规模的晶圆上使用。因此,晶圆尺寸高达 12 英寸的 GaN-on-Si 具有优势。6 英寸的 GaN-on-sapphire 相对便宜;然而,许多代工厂不接受蓝宝石,其导热性较差。

为了生长高质量的 GaN,需要昂贵的衬底,例如块体 GaN 和 SiC。因此,器件制造的生产成本明显高于硅基电子产品。为了实现具有成本效益的先进 GaN 功率器件性能,同时有效地管理产生的热量,可以从衬底上去除外延层,从而实现衬底的重复使用,并直接结合到散热器上以提高器件的热性能。然而,现有的去除工艺,例如涉及光电化学蚀刻、机械剥落和激光界面分解的去除工艺,加工速度慢和/或表面粗糙/开裂明显,限制了基板重复使用的工艺产量和实用性。因此,这些传统方法的工艺成本通常超过 GaN 衬底成本,

当器件需要更好的质量时,就位错密度、热性能和汽车、射频和数据中心应用中的高压器件所需的更高频率而言,GaN-on-SiC 往往是最佳选择去。

然而,GaN-on-SiC 是一种昂贵的解决方案。一旦在 SiC 衬底上生长出高质量的 GaN 外延层,您将获得更好的用于功率和射频应用的 GaN 器件。缺点是SiC衬底非常昂贵。GaN外延层在其上生长后不再需要SiC衬底。

总结一下:

当前技术的大型 GaN 晶片具有较高的位错密度(结晶度差)。

GaN-on-Si 晶圆倾向于使用非常厚的缓冲层和中间层来管理应力,从而难以管理导热性。

大多数其他基板都非常昂贵,并且无法选择更大的晶圆。

有哪些新技术可以帮助解决这些问题?

到目前为止,还没有简单的方法从这种器件结构中去除 SiC 或 Si 衬底,因此该器件非常昂贵。

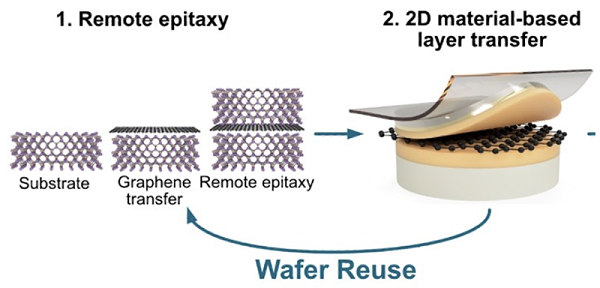

美国麻省理工学院远程外延和二维材料层转移(2DLT)技术的发明使得通过二维材料生长复合材料成为可能。生长后,可以将其提起以从中释放基材并重复使用。

借助这项技术,人们可以创建 GaN 外延层并将其从昂贵的 SiC 衬底上剥离,然后将其转移到低成本衬底上。这将释放 SiC 衬底,以便在下一个 GaN Epi 晶圆生长中重复使用(参见图 1)。

远程外延和 2DLT 解决方案的优势在于 GaN 薄膜的瞬时剥离,无需任何抛光或其他后处理步骤。粘合或剥离过程不会引入多晶或非晶区。不需要结晶度差的成核层,因此可以获得超薄(<200 nm)GaN独立膜。这是任何其他现有技术都无法实现的。

GaN的新时代已经开始。远程外延和 2DLT 使该技术能够将 GaN 扩展到更大的尺寸,通过降低位错密度来提高质量,并帮助以低成本管理热特性

深圳市晶光华电子有限公司 26年专注提供一站式晶振产品解决方案,产品主要有SMD石英晶振、 车规晶振 、 SMD振荡器等。晶光华始终坚持以品质为基石,品质符合国际IEC和美国ANSI标准。为了满足客户的高标准需求,我司积极整合供应链,真正服务每一位品质客户。

本文标签: 用于高压 GaN 器件的 GaN Epi 晶圆制造 琻捷TPMS-SNP705胎压监测传感芯片 晶光华晶振 振荡器 车规级晶振