什么是锁相环? 大多数人都听过“锁相环”(PLL)这个词,然而很少有人真的了解到底什么是 PLL ,在本文中对基本 PLL 特性提供了清晰、直观的解释。

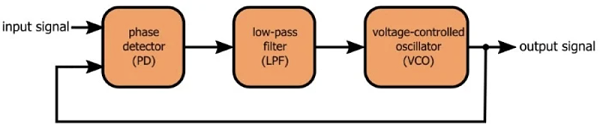

“锁相环”出现在各种环境中:微控制器、射频解调器、振荡器模块、串行通信。首先要了解的是,“PLL”并不是指单个组件。PLL 是一个系统,它由多个组件组成,这些组件经过精心设计并以负反馈配置互连。PLL 确实是作为单个集成电路出售的,因此将它们视为“组件”是很自然的。

PLL ≥ PD + LPF + VCO

这与 PLL 一样基本。让我们讨论三个基本组成部分。

相位检测器,不是真正的相位检测器,但这是标准术语。PLL中的相位检测器实际上是一个相位差检测器,即它接受两个周期性输入信号并产生一个代表两个输入之间相位差的输出信号。

相位检测器的输出不是与相位差成正比的直接模拟信号。直接的模拟信号就在某处,但它与高频内容相结合,使信号看起来与你的预期大不相同。因此,低通滤波器。它抑制高频分量并将鉴相器的输出转换为可以控制 VCO 的东西。

压控振荡器是由电压控制的振荡器,更具体地说,振荡器产生的周期信号的频率由电压控制。因此,VCO 是一个可变频率振荡器,它允许外部电压影响其振荡频率,在 PLL 的情况下,控制电压是经过低通滤波的相位检测器信号。

波形

由数字 PLL 产生的一些波形,你可能将 PLL 设想为一个主要的模拟系统,也许用数字系统进行试验更简单,重要一点是,相同的概念适用于模拟和数字实现,如果你了解这些数字波形,那么你通常会了解 PLL 信号。

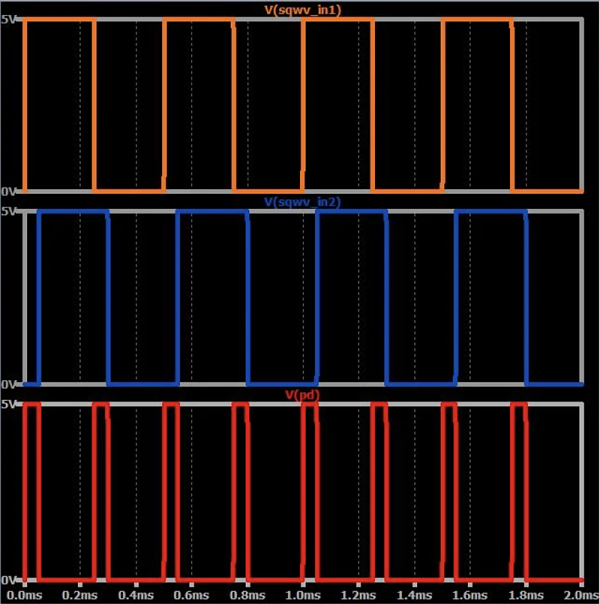

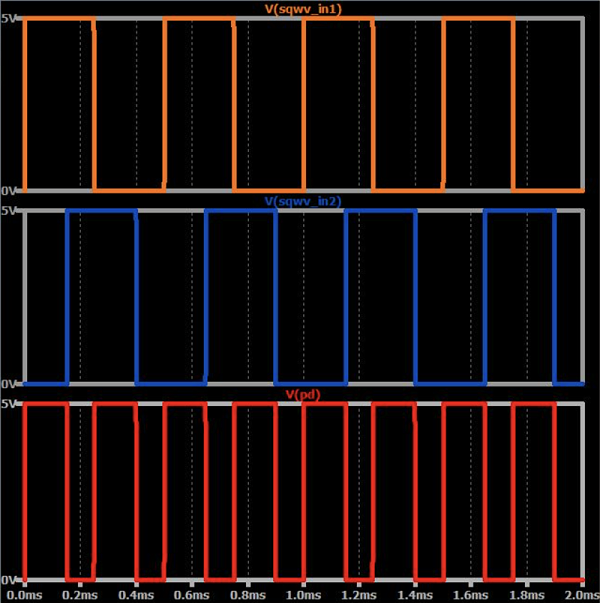

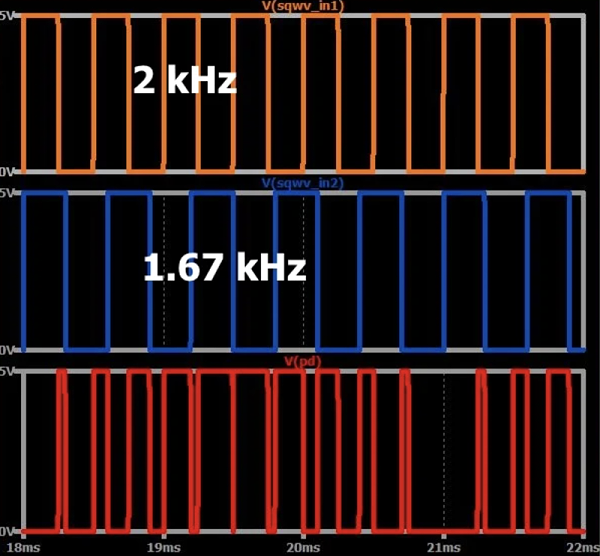

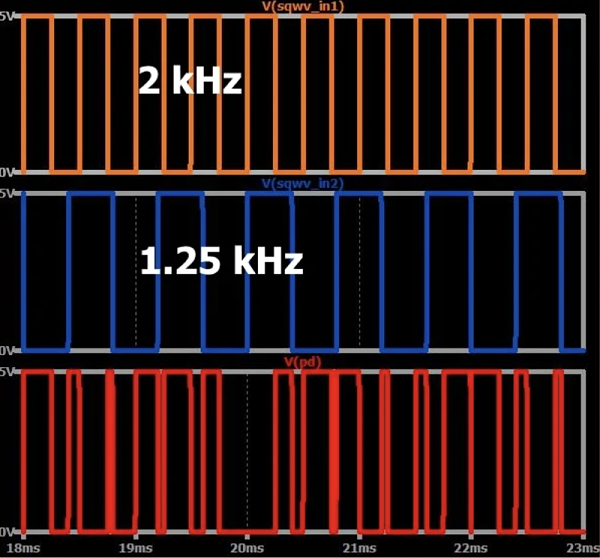

在数字 PLL 中,相位检测器只需要一个 XOR 门。只有当两个输入不同时,异或门才会产生逻辑高输出,如果将此行为扩展到两个输入均为方波的情况,则 XOR 将成为“异相检测器”。

这两个方波具有很小的相位差,因此它们在周期的一小部分处于不同的逻辑状态,当逻辑状态不同时,XOR 输出为高,如果相位差变大,XOR 输出将更长时间处于逻辑高电平。

这就是 XOR 门用作相位检测器的方式,随着相位差的增加,输出在逻辑高电平上花费了大部分周期,换句话说,XOR 输出的占空比和平均值与相位差成正比。

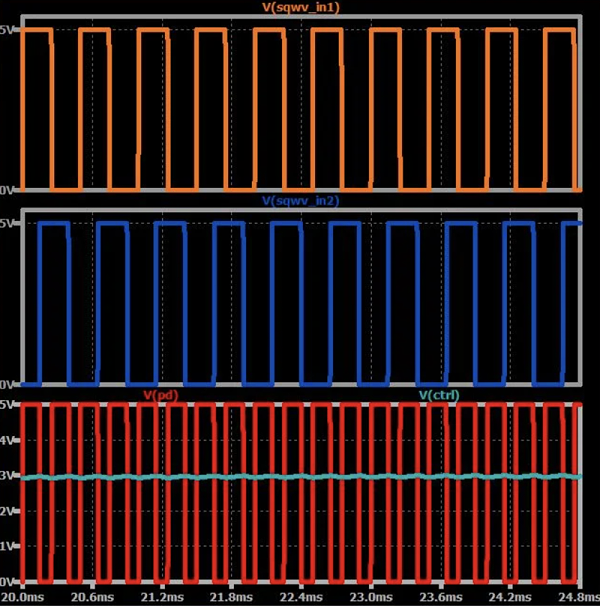

下一步是使用这个平均值作为 VCO 的控制信号,这就是低通滤波器发挥作用。

绿色线是带有一点纹波的平均值,是通过将相位检测器信号通过一个简单的 RC 低通滤波器产生的(如果你使用过“ PWM DAC ”,你可能会认出这种技术,是一种数模转换器,通过对脉宽调制信号进行低通滤波来发挥作用)。迹线被标记为“ctrl”,因为这是我们可以用来控制(即改变频率)VCO 的信号。

关闭循环

PLL 可以以各种巧妙的方式使用,但基本功能是将输出频率“锁定”到输入频率。(它们还将输出相位锁定到输入相位,正如你从名称“锁相环”中所看到的那样,但它是一种不同类型的锁定。)锁定动作是通过负反馈实现的,即通过路由输出信号返回到相位检测器(如上图所示)。

当两个输入频率相等时(如上例所示),相位检测器才会产生恒定的占空比(因此产生恒定的平均值)。不同的频率会导致占空比的周期性变化。

因此,控制电压将继续上下波动,直到输出频率等于输入频率。

要建立锁定,PLL 必须做的不仅仅是使输出频率等于输入频率。它还必须建立导致适当控制电压的输入-输出相位关系。

PLL 无法直接控制 VCO 信号的相位。它可以调整 VCO 相位的唯一方法是调整频率,因此频率变化将继续,直到实现锁频和锁相。

结论

本文介绍了锁相环的基本结构和一些操作细节,它是一个基于负反馈的系统,可以生成锁定并跟踪输入信号频率的周期性信号。

深圳市晶光华电子有限公司 26年专注提供一站式晶振产品解决方案,产品主要有SMD石英晶振、 车规晶振 、 SMD振荡器等。晶光华始终坚持以品质为基石,品质符合国际IEC和美国ANSI标准。为了满足客户的高标准需求,我司积极整合供应链,真正服务每一位品质客户。

本文标签: 什么是锁相环 PLL 晶光华晶振 压控振荡器 车规级晶振 集成电路 振荡频率