【晶光华课堂】晶振输出信号类型有哪些? 晶振输出信号类型可以提供不同的优点和缺点,这取决于你用在什么产品上,重要的是要知道信号类型,避免时钟信号的衰减和失真。那么晶光华小编今天为大家介绍一下关于晶振输出信号都有哪些:

单端输出:

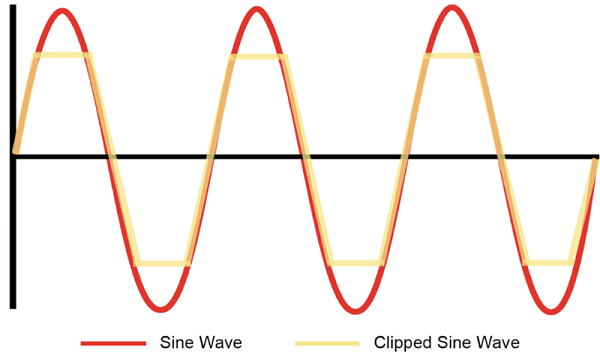

※Sinewave(正弦波):这是晶振的自然默认信号输出。它仅由一个基本的正弦频率输出组成(不存在任何谐波),正弦波输出非常适合要求苛刻的低相位噪声应用。

※Clipped Sinewave(削峰正弦波):通过限制信号输出,防止波形达到正常的高点或低点,这样做可以在不牺牲任何相位噪声的情况下创建一个方波输出。这通常是TCXO的输出波形。

※CMOS【Complementary Metal Oxide Semiconductor】(互补金属氧化物半导体电路)

※HCMOS【High Speed CMOS】(高速互补金属氧化物半导体电路)

※LVCMOS【Low Voltage CMOS】(低压互补金属氧化物半导体电路)

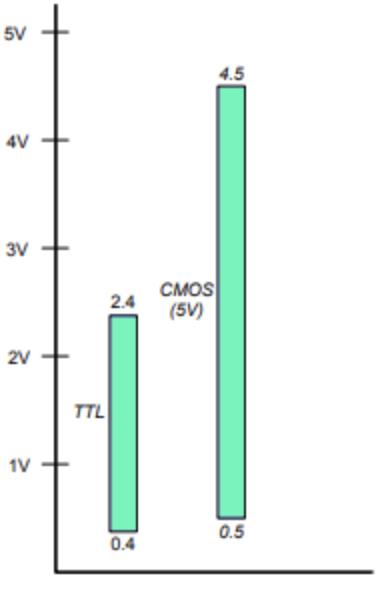

CMOS和HCMOS以及 LVCMOS 都属于互补金属氧化物半导体类别。它们是方波数字输出,最适合低频时钟,通常低于250 MHz。这将允许时钟输出和芯片输入之间的直接连接。在大多数情况下,可以使用低阻值串联电阻来有效减少信号反射并保持可靠的信号完整性。

※TTL【Transistor to Transistor Logic】(晶体管-晶体管逻辑电路):这是一种较旧的输出方式,大部分已被CMOS所取代,这是因为CMOS提供了比TTL更低的成本和更好的抗噪声性能。CMOS和TTL 都非常适合低功耗、更高的输出幅度,并且成本相对较低。

差分输出:

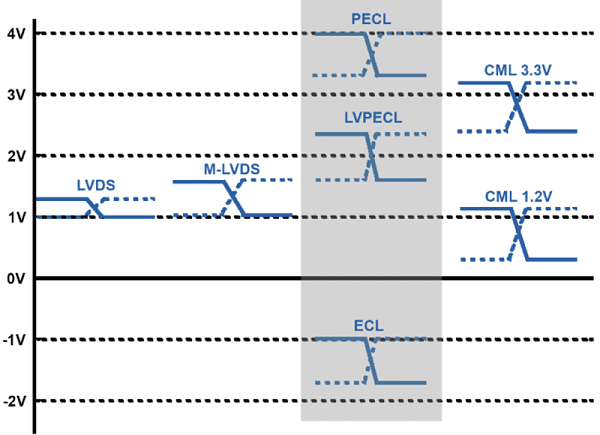

※ECL【Emitter Coupled Logic】(发射极耦合逻辑电路):ECL主要是作为TTL的替代品引入的,ECL电路可以非常迅速地改变状态,更有能力满足非常高速的数据传输需求;缺点则是ECL需要相当高的电流才能运行,ECL在使用过程中也使用负电源,当尝试连接到正基电源设备时,这可能会带来挑战。

※PECL【Positive Emitter Coupled Logic】(正发射极耦合逻辑电路):PECL输出常用于高速时钟分配电路。这是因为PECL提供了高抗噪性、在长线路长度上驱动高数据速率的能力,以及由于大电压幅度带来的良好抖动性能,所以PECL需要高功耗才能运行。

※LVPECL【Low Voltage PECL】(低电压正发射极耦合逻辑电路):LVPECL 为千兆以太网和光纤通道的使用提供了良好的基础。LVPECL在电气上类似于LVDS,但提供更大的差分电压幅度和略低的功率效率,此外不同品牌可能出现不同的输入公差。

※CML【Current-Mode Logic】(电流模式逻辑电路):CML与LVPECL具有相似的性能,主要区别是CML不需要外部偏差,因此CML在低功耗情况下成为LVPECL的较好替代品。

※LVDS【Low Voltage Differential Signaling】(低电压差分信号):LVDS 与 LVPECL 输出类似,但LVDS功耗更低,电压波动也更小。LVDS 通常用于满足高速数据传输需求,例如时钟分配或背板收发器。对于更高的数据速率,通常需要HCSL、CML或 LVPECL,但比LVDS 需要更大的功耗。其他优点包括降低对噪声的敏感性,并且易于在CMOS IC中实现。 与PECL相比,LVDS的一个缺点是其抖动性能降低,但正在研究的新技术将实现与LVPECL相同水平的抖动性能。

※HCSL【High Speed Current Steering Logic】(高速电流转向逻辑电路):HCSL有一个更新的输出标准,类似LVPECL。HCSL的优点之一是其高阻抗输出和快速转换时间。建议使用10至30欧的串联电阻以减少可能的过冲和振铃。其他优势包括最快的切换速度、低功耗(介于LVDS和LVPECL之间)以及平均良好的相位噪声性能。

深圳市晶光华电子有限公司专注石英晶振生产26年,强大的专业团队,服务超过5000+客户,年产能6亿PCS,1天试样,3天测试,1周交货;如果您对我们的石英晶振感兴趣,欢迎咨询我们的客服,获取详细资料,我们将为您提供专业贴心的服务。

本文标签: 晶振输出信号类型有哪些 正弦波 削峰正弦波 方波 晶光华 TCXO 差分输出 CMOS LVDS